- #1

jSwathi

- 16

- 1

<Moderator's note: Thread split from another thread as the posts essentially comprise a new question about a new circuit. The problem statement has been formed by combining two of the moved posts. Poster has been notified to create a new thread for a new question>

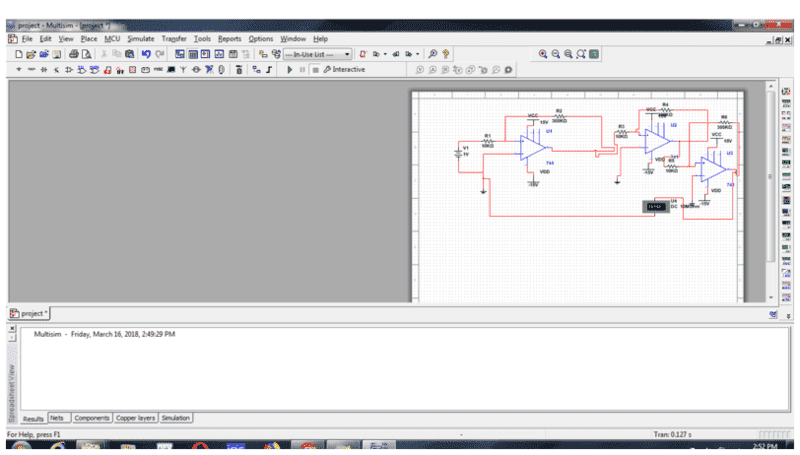

1. Homework Statement I am using three-stage cascading amplifier, I used resistors of 10K and 300K with the input voltage of 1V. My aim is to get 30 for each stage and calculated bandwidth is around 33.33KHz. Now, when I am simulating at the end of the third amplifier I am getting the output of 15V which I measured in voltmeter. Is this the right method or should I need capacitors in this? Help me out

I have attached my file below

I have a question, Output coming from two stages would saturate the third op-amp or it produces the output

1. Homework Statement I am using three-stage cascading amplifier, I used resistors of 10K and 300K with the input voltage of 1V. My aim is to get 30 for each stage and calculated bandwidth is around 33.33KHz. Now, when I am simulating at the end of the third amplifier I am getting the output of 15V which I measured in voltmeter. Is this the right method or should I need capacitors in this? Help me out

I have attached my file below

I have a question, Output coming from two stages would saturate the third op-amp or it produces the output

Attachments

Last edited by a moderator: