- #1

jisbon

- 476

- 30

- Homework Statement

- -

- Relevant Equations

- -

Hi all,

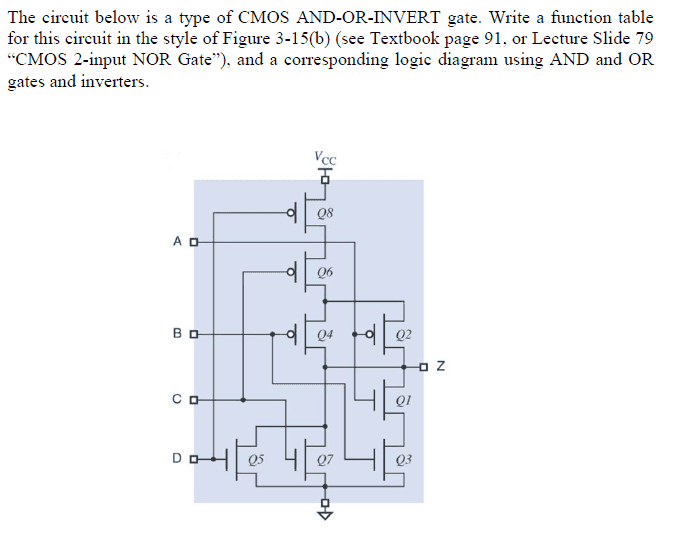

Having some problems digesting on electric circuits. Below is an example of a question and I would like to ask how do I go ahead in solving this.

Firstly, for these types of questions:

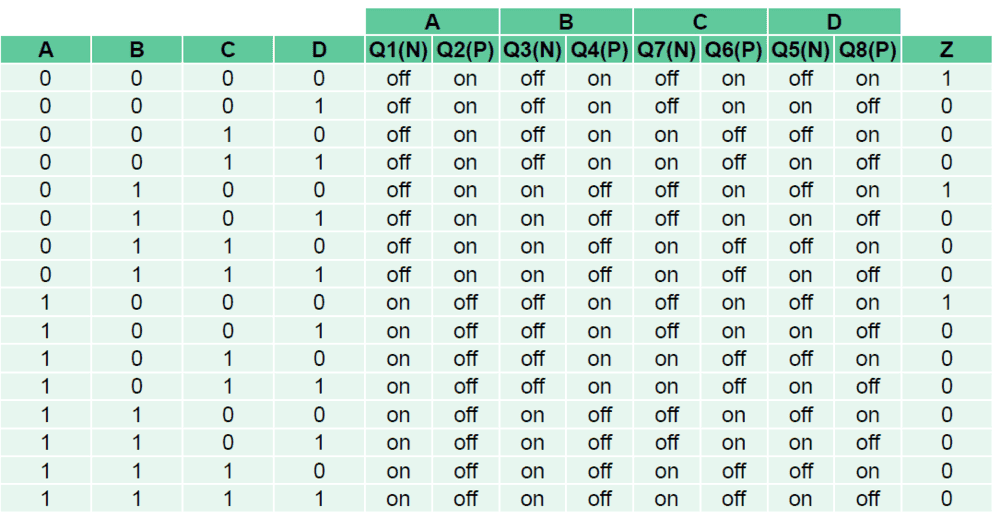

I have understood how to write a function table, and it goes something like this:

Now what I am having problems with is constructing the equation and the logic circuit. I searched online and found that the equation is simply the sum of all the variables that will give a HIGH, which in this case, is z = A'B'C'D' + A'BC'D' + AB'C'D'

Is this correct?

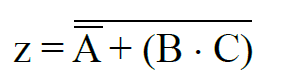

If it is, how do I then determine how the logic circuit should be drawn? I'm pretty confused on how do I even start one.As for the second question, it is simply (I guess a reverse) of the above question. It tells me to design a CMOS circuit given an equation:

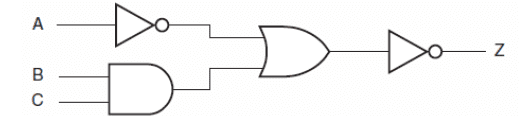

I managed to derive the logic circuit based on the equation, which is:

Now,how do I draw the CMOS circuit? Quite overwhelmed :/

Anyone who can refer me to some videos/reading materials on this would be great. I don't understand how do I simply draw one :/

Thanks!

Having some problems digesting on electric circuits. Below is an example of a question and I would like to ask how do I go ahead in solving this.

Firstly, for these types of questions:

I have understood how to write a function table, and it goes something like this:

Now what I am having problems with is constructing the equation and the logic circuit. I searched online and found that the equation is simply the sum of all the variables that will give a HIGH, which in this case, is z = A'B'C'D' + A'BC'D' + AB'C'D'

Is this correct?

If it is, how do I then determine how the logic circuit should be drawn? I'm pretty confused on how do I even start one.As for the second question, it is simply (I guess a reverse) of the above question. It tells me to design a CMOS circuit given an equation:

I managed to derive the logic circuit based on the equation, which is:

Now,how do I draw the CMOS circuit? Quite overwhelmed :/

Anyone who can refer me to some videos/reading materials on this would be great. I don't understand how do I simply draw one :/

Thanks!

Attachments

Last edited by a moderator: