techn0

- 19

- 5

- TL;DR Summary

- Need help getting high side gate working properly.

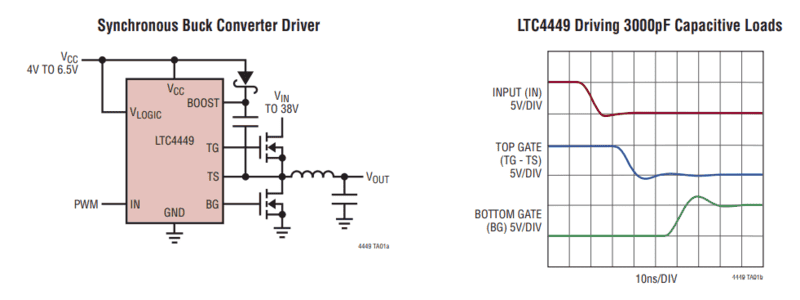

I have designed a circuit utilizing a LTC4449 high speed n-chan mosfet driver.

I am running the Vcc at 5 v from a 0.5a linear regulator 7805 type.

The switching voltage is 24v from 600w smps.

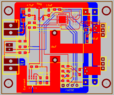

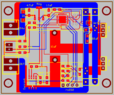

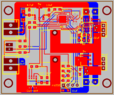

I am using this exact layout. The gate driving on the bottom mosfet seems to be working properly but the gate drive on the top does not. I think it is an issue with the boost circuitry.

The Schottky diode I am using is ACDBN1100-HF 100V

The boost cap is C1206C224M5UAC7800 0.22uF

I have tried several input pwm frequencies from 15k to 250k with no change.

It is my understanding that a high gate singal on the top mosfet is going to be 24v plus 5v. When I measure boost pin voltage it is just around 5v. Should it be 24v or 29v?

This component is a 2mm x 3mm DFN so it is ultra small and hard to work with. I have resoldiered it serveral times in an attempt to get this circuit working correctly and replaced it once. It appears to be soldered properly.

Thanks in advance for everyone's help.

I am running the Vcc at 5 v from a 0.5a linear regulator 7805 type.

The switching voltage is 24v from 600w smps.

I am using this exact layout. The gate driving on the bottom mosfet seems to be working properly but the gate drive on the top does not. I think it is an issue with the boost circuitry.

The Schottky diode I am using is ACDBN1100-HF 100V

The boost cap is C1206C224M5UAC7800 0.22uF

I have tried several input pwm frequencies from 15k to 250k with no change.

It is my understanding that a high gate singal on the top mosfet is going to be 24v plus 5v. When I measure boost pin voltage it is just around 5v. Should it be 24v or 29v?

This component is a 2mm x 3mm DFN so it is ultra small and hard to work with. I have resoldiered it serveral times in an attempt to get this circuit working correctly and replaced it once. It appears to be soldered properly.

Thanks in advance for everyone's help.