madaari

- 5

- 0

Hi forums,

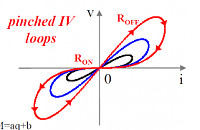

Following is the hysteresis loop of a standard memristor:

Please note that, the red one is for lowest frequency and black for highest frequency.

From the graph, one can take the following observations:

1> As frequency increases, area of graph decreases

2> With increase in frequency, graph tends to tilt more towards x axis

3> Slight deformity of the red curve at higher VI values.

I tried interpreting these observations, keeping in mind memristors Piecewise linear model(Is that a correct assumption?).

If second observation is correct:- Memristance decreases with increase in frequency and at frequency tending to infinity, it acts like a constant value resistance whose value should be Minimum possible value of memristance. Right?

Also, I need a bit explanation for observation number 3(about deformity). I'm unable to figure out it's reason.

Thanks,

[moderator edited out the OP's name and cross posting info.]

Following is the hysteresis loop of a standard memristor:

Please note that, the red one is for lowest frequency and black for highest frequency.

From the graph, one can take the following observations:

1> As frequency increases, area of graph decreases

2> With increase in frequency, graph tends to tilt more towards x axis

3> Slight deformity of the red curve at higher VI values.

I tried interpreting these observations, keeping in mind memristors Piecewise linear model(Is that a correct assumption?).

If second observation is correct:- Memristance decreases with increase in frequency and at frequency tending to infinity, it acts like a constant value resistance whose value should be Minimum possible value of memristance. Right?

Also, I need a bit explanation for observation number 3(about deformity). I'm unable to figure out it's reason.

Thanks,

[moderator edited out the OP's name and cross posting info.]

Attachments

Last edited: