- #1

DrOnline

- 73

- 0

NB: Got a bit wordy, highlighted question in red.

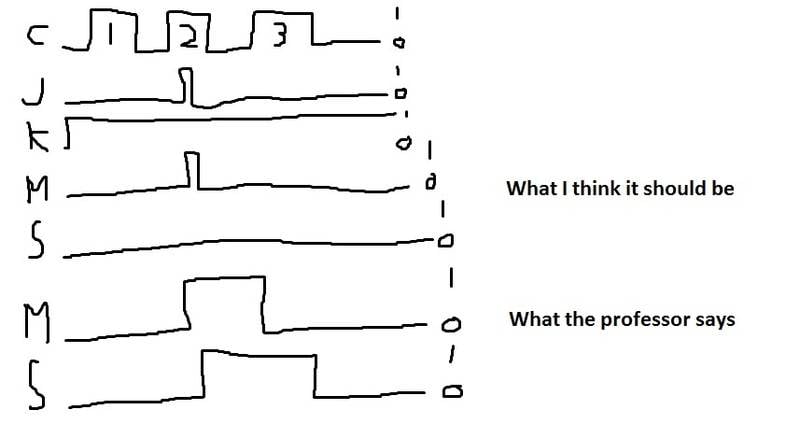

Just a picture of what we're dealing with.

I'm given a clock pulse, J and K inputs, and asked to describe the JK master-slave flip flop output.

J K Q(t+1)

0 0 Q(t) No change

0 1 0 reset

1 0 1 set

1 1 Q'(t) Complement

I understand:

Clock = 1 -> Master value can be modified by changes to J and/or K

Clock = 0 -> Value of Slave is set to that of Master

Sorry for the drawing, I hope it is sufficient. During the positive clock phase I called 2, there is a brief blip in the J.

J & K are both 1, so I complement the Master value. it is now 1.

Now here is where I get uncertain. As I understand it, ANY change in J and/or K, even if there are 1000 changes, during a positive clock phase, will be reflected in the master. So only the FINAL value, once the clock drops from 1 to 0, in the master, "sticks".

So I say: that blip in J, well it drops quickly, during a positive clock phase, and so that leaves us with J = 0, K = 1, which is reset, so I drop the Master to 0 again.

However, this professor:

(skip to 4:10)

he's got an image from a book that says: "...something tricky about the master-slave, it's called the "one's catcher", it remembers any activity on the J or K while the clock is high. The J went high, then it went low, but it remembers".

It remembers? Can somebody explain how it remembers?

Homework Statement

Just a picture of what we're dealing with.

I'm given a clock pulse, J and K inputs, and asked to describe the JK master-slave flip flop output.

Homework Equations

J K Q(t+1)

0 0 Q(t) No change

0 1 0 reset

1 0 1 set

1 1 Q'(t) Complement

The Attempt at a Solution

I understand:

Clock = 1 -> Master value can be modified by changes to J and/or K

Clock = 0 -> Value of Slave is set to that of Master

Sorry for the drawing, I hope it is sufficient. During the positive clock phase I called 2, there is a brief blip in the J.

J & K are both 1, so I complement the Master value. it is now 1.

Now here is where I get uncertain. As I understand it, ANY change in J and/or K, even if there are 1000 changes, during a positive clock phase, will be reflected in the master. So only the FINAL value, once the clock drops from 1 to 0, in the master, "sticks".

So I say: that blip in J, well it drops quickly, during a positive clock phase, and so that leaves us with J = 0, K = 1, which is reset, so I drop the Master to 0 again.

However, this professor:

(skip to 4:10)

he's got an image from a book that says: "...something tricky about the master-slave, it's called the "one's catcher", it remembers any activity on the J or K while the clock is high. The J went high, then it went low, but it remembers".

It remembers? Can somebody explain how it remembers?

Last edited by a moderator: