- #1

jaus tail

- 615

- 48

Hi,

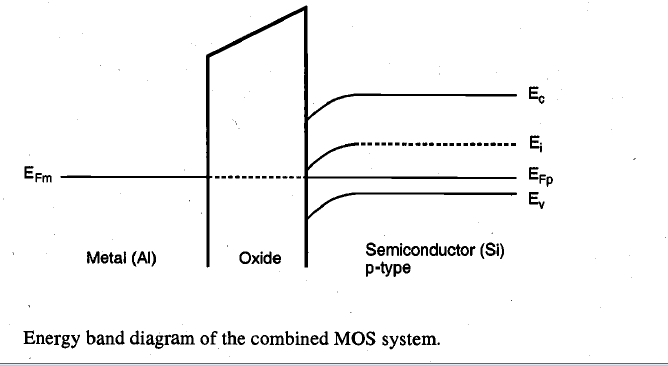

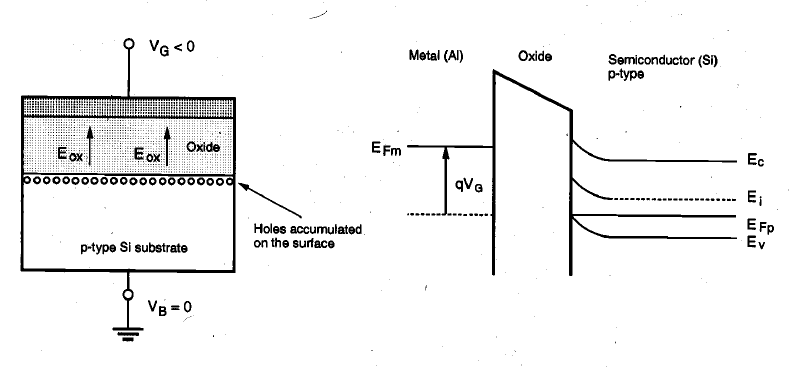

I'm studying MOSFET and the book says that when N-channel mosfet has negative or positive gate voltage, the energy band diagram will shift. I don't understand why Efm shifts.

Now when Vg is negative the Efm shifts upwards, Why? And when later when Vf is positive the Efm also shifts again? I don't understand this. Shouldn't Efm and Efp be at same level?

I'm studying MOSFET and the book says that when N-channel mosfet has negative or positive gate voltage, the energy band diagram will shift. I don't understand why Efm shifts.

Now when Vg is negative the Efm shifts upwards, Why? And when later when Vf is positive the Efm also shifts again? I don't understand this. Shouldn't Efm and Efp be at same level?