- #1

haminous

- 7

- 0

Greetings. I am trying to understand the common base amplifier better so I can build a preamp for a low impedance guitar pickup. In order to explore its operation, I tried to model it with the "approximated" Ebers-Moll model (from the wikipedia page on BJT's) and the graphing program in Mac OSX.

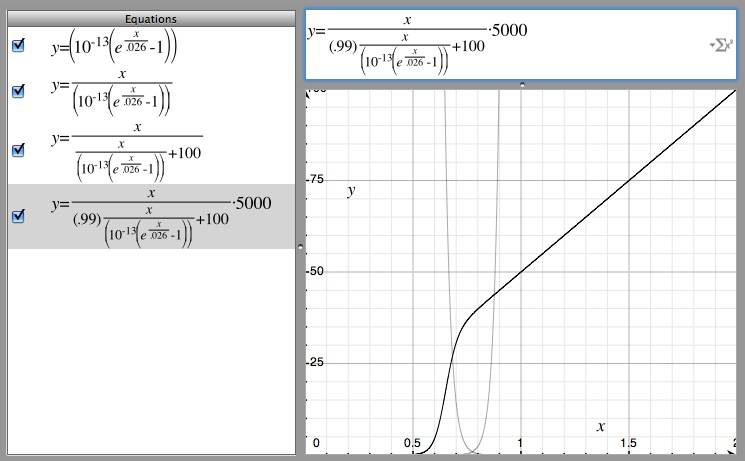

The first equation is the emitter current (Y) relationship to base-emitter voltage (X). The second puts (X) over that equation to give the resistance. The third adds 100 ohms (as the input resistor) and puts (X) over the that again to give the new base current. The fourth and highlighted equation is supposed to be the collector current (with the addition of the 0.99 coefficient for alpha) times the output resistor to give the input to output voltage relationship. This was supposed to be a very generic and ideal model (hence the lack of base-emitter resistance or accounting for saturation) just for me to visualize what is going on and play with the numbers. But, as you can see, the graph does not look like what it should. There is a steep rise over about 0.6 to 0.8 volts and then a slope that looks like is has about the right gain, just shifted up way too high. Where does that steep rise and offset come from as opposed to a regular transistor model? Is it due to over-simplification? I would really like to understand the mathematical relationships here.

I am also extremely curious why, according to the author of this site: http://www.allaboutcircuits.com/vol_3/chpt_4/7.html" , changing the DC bias changes the base-emitter resistance, thus affecting the gain.

And, finally, if anyone can provide some insight... What would be the advantages and disadvantages of using either a FET in the common gate arrangement or an inverting opamp with a low input impedance?

Thanks in advance for your time.

The first equation is the emitter current (Y) relationship to base-emitter voltage (X). The second puts (X) over that equation to give the resistance. The third adds 100 ohms (as the input resistor) and puts (X) over the that again to give the new base current. The fourth and highlighted equation is supposed to be the collector current (with the addition of the 0.99 coefficient for alpha) times the output resistor to give the input to output voltage relationship. This was supposed to be a very generic and ideal model (hence the lack of base-emitter resistance or accounting for saturation) just for me to visualize what is going on and play with the numbers. But, as you can see, the graph does not look like what it should. There is a steep rise over about 0.6 to 0.8 volts and then a slope that looks like is has about the right gain, just shifted up way too high. Where does that steep rise and offset come from as opposed to a regular transistor model? Is it due to over-simplification? I would really like to understand the mathematical relationships here.

I am also extremely curious why, according to the author of this site: http://www.allaboutcircuits.com/vol_3/chpt_4/7.html" , changing the DC bias changes the base-emitter resistance, thus affecting the gain.

And, finally, if anyone can provide some insight... What would be the advantages and disadvantages of using either a FET in the common gate arrangement or an inverting opamp with a low input impedance?

Thanks in advance for your time.

Last edited by a moderator: