brainbaby

- 232

- 5

Dear friends,

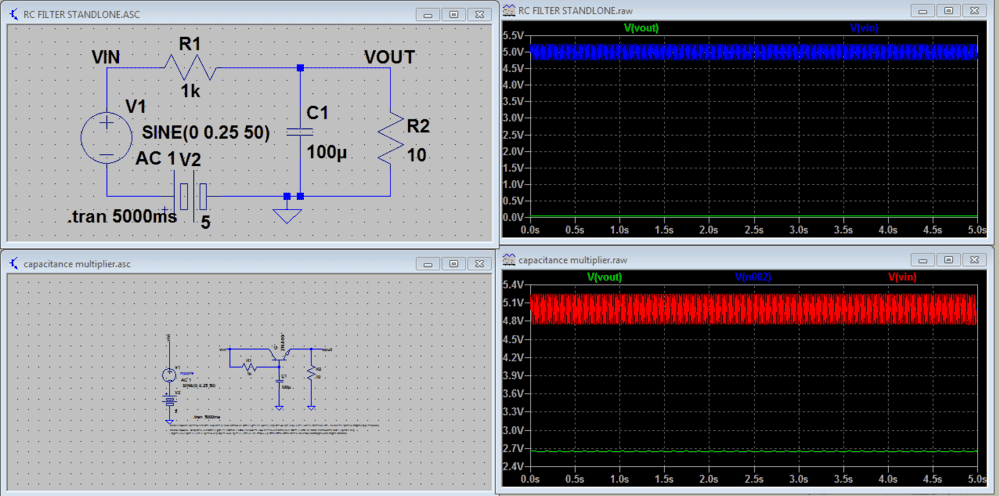

I am simulating a capacitance multiplier circuit and an RC filter circuit simultaneously. My aim is to check the reduction in ripples when using a cap multiplier circuit against an RC filter.

I am familiar with ltspice but not quite an expert. I am comparing two output waveforms of both the circuits.

Can someone tell me how measure how much ripple has been reduced when cap multiplier is used. How to view that in simulation.??

.asc files have been attached below.

Thank you!

I am simulating a capacitance multiplier circuit and an RC filter circuit simultaneously. My aim is to check the reduction in ripples when using a cap multiplier circuit against an RC filter.

I am familiar with ltspice but not quite an expert. I am comparing two output waveforms of both the circuits.

Can someone tell me how measure how much ripple has been reduced when cap multiplier is used. How to view that in simulation.??

.asc files have been attached below.

Thank you!