Mathhhew said:

What happened to the two capacitor I previously had in serie with R1 and R2? Were they useless?

The series C made it too difficult to identify what was influencing the response. They also caused the unreal AC floating island that later needed to be ground referenced with the 1G+1G resistors. The complexity increased again when your signal source had a fixed hidden internal resistance that was not compatible with all signal and power applications of CM chokes.

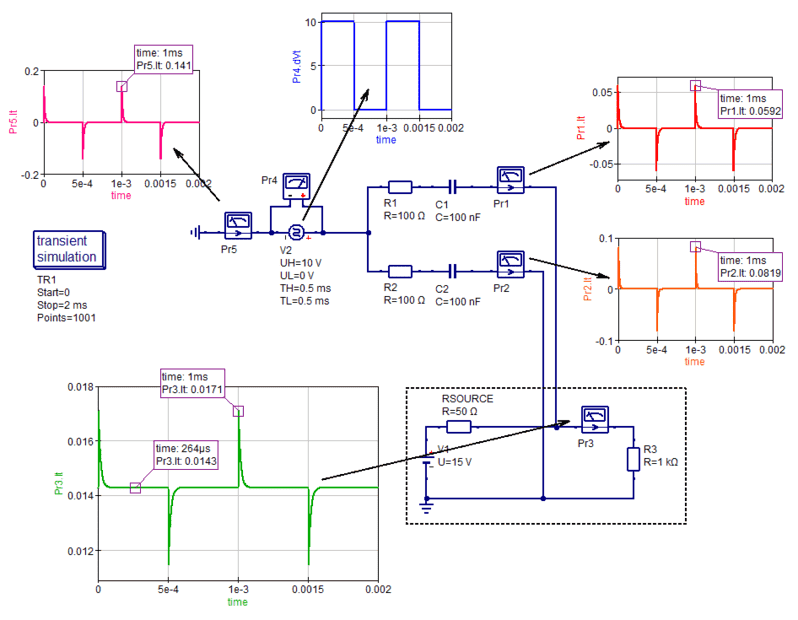

As an example of making it simpler, in the latest circuit you post in #13, there is a low impedance voltage source, V2, driving R2+C2 against ground, and you are measuring the V2 current, which is confounded by the addition of that unnecessary frequency dependent current component.

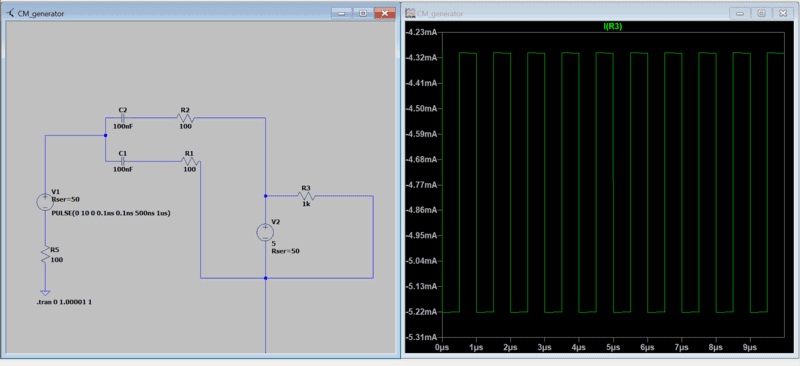

I directly generate and sum two low impedance voltages, that are opposite phases of the signal, but have identical common mode noise. The series Rs in my circuit represents the impedance of the source and cables. The inductance of the CM choke can be selected, with additional components if needed. The output load, Rd, can be chosen to represent the appropriate signal input or low impedance power supply rails that are being driven by your CM choke model.

I have now changed my load to use a centre-tap grounded pair of load resistors. That makes for symmetry, so only one output resistor (Rd) needs to be considered, which corrects for the +3 dB double signal source. Set the parameters of the model with “.param Rs=1 Lt=2m Rd=100”. Now that the source impedance R+C has been eliminated, it is the ratio of only those three parameters that represent the real world circuit and determine the transfer function of the CM choke being modeled over the specified AC frequency range.

Mathhhew said:

But I don't have these oscillations, my filtered signal is smooth right away, and I don't understand why.

Probably because the 10 uF output caps swamp the 100 nF coupling caps, making the input more like a current source. The resonant frequency is decided by choke Lt and the two coupling caps, while oscillation is damped by the load resistance.

P.S. Note that a square wave with longer rise and fall times will have less high frequency energy and so will cause less ringing.